我们经常看到报道上说芯片制程达到了14nm、7nm、5nm,最近中芯国际在没有ASML的EUV光刻机的情况下,实现了7nm的制程,有很多人对此感到很兴奋。同时也有人问,半导体的多少纳米制程,到底是指晶体管间距多少纳米,还是晶体管的大小是多少纳米?

要回答这个问题,我们得从一个晶体管单位的组成说起。

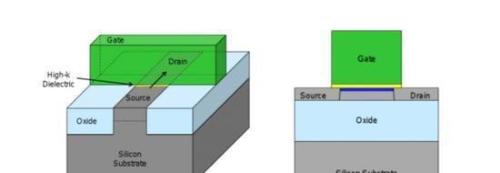

一个晶体管结构大致如下图所示:

晶体管工作的时候,电流从源极(Source)流入漏极(Drain),中间绿色的那堵墙叫作栅极(Gate),相当于一个闸门,它负责控制源极和漏极之间电流的通断。而电流通过栅极(Gate)时会损耗,栅极的宽度就决定了损耗的大小。表现在芯片上,就是芯片的发热和功耗,栅极越窄,芯片的功耗就越小。

栅极的最小宽度(栅长,就是上面右图Gate的宽度)就是多少nm工艺中的数值了。

在实际芯片制程工艺中,越小的制程工艺,不但对制造工艺和设备有更高的要求,其芯片性能也会受到极大的影响。当宽度逼近20nm的时候,栅极对电流的控制能力就会急剧下降,从而发生“漏电”的问题。

漏电会导致芯片的功耗上升,更会使电路发生错误,信号模糊。为了解决信号模糊的问题,芯片又不得不提高核心电压,使得功耗更大。这对于更小工艺制程来说,是一个矛盾。

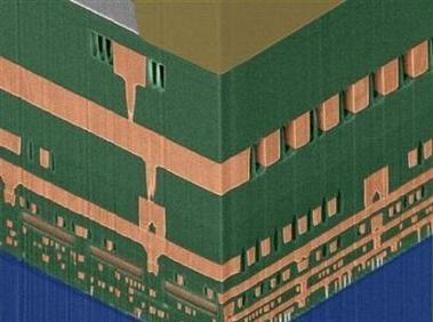

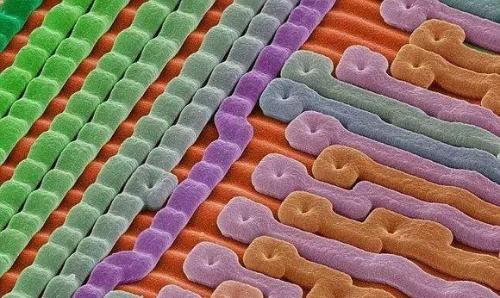

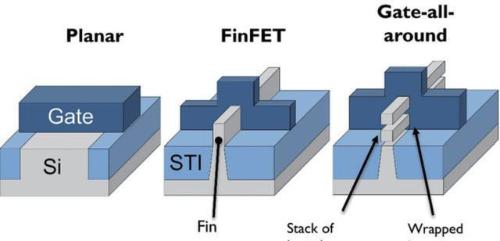

为了解决这个问题,台积电和三星等芯片制造企业,提出了FinFET工艺。这种工艺,简单来说,就是将芯片内部平面的结构,变成了立体的,把栅极形状改制,增大接触面积,减少栅极宽度的同时降低漏电率,而晶体管空间利用率大大增加。

FinFET(鳍式场效应晶体管),是一种新型的晶体管,这种被称为CMOS的工艺优势很明显,很快就被大规模应用于手机芯片上。

然而,在5nm以下的制程芯片中,影响芯片性能的除了漏电问题之外,更大的是量子效应的影响,这时芯片的特性更难控制,科学家们要寻求新工艺才能使芯片更进一步。

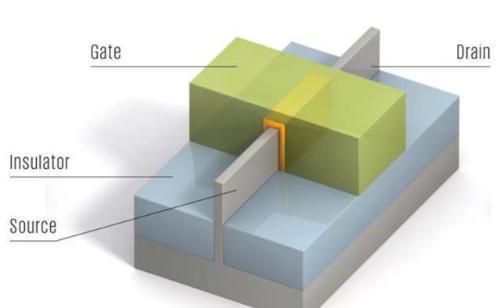

业内正在发展的一种新技术叫做环绕式栅极技术(Gate-All-Around),简称为GAA横向晶体管技术(GAAFET)。这项技术的特点是实现了栅极对沟道的四面包裹,源极和漏极不再和基底接触,而是利用线状(可以理解为棍状)或者平板状、片状等多个源极和漏极横向垂直于栅极分布后,实现MOSFET的基本结构和功能。

- 德国突然宣布不再使用华为设备,任正非的回应略显“无奈心酸”!

- 总裁夫人手撕张大奕最新进展!天猫少帅道歉,阿里巴巴正式调查

- 央视关注!格力“猎手”核心科技为全球防疫而战

- 程序员感慨:入职20W每年20W增长,大厂和小厂比,那就是天上人间!

- 程序员大牛入职不久,把公司效率提升一大截,结果老板开始裁员了

- 一加8 Pro首销1分钟破亿,三大核心亮点!

- 小米新系统即将登场,流畅度堪比苹果iOS,23款机型优先升级

- 3D打印能否填补抗疫医疗设备的缺口?

- iQOO Neo 3 GeekBench跑分曝光 144Hz高刷865新旗舰

- 数字人民币真的来了?央行回应

- 自食其果!总裁出轨网红被调查降职,马云接班人要另换他人

- “国产芯片”新黑马诞生!华为喜从天降,台积电也不再沉默了

- 重磅!8万人拿不回本金 号称有2.2亿人用户的随手记倒下了!

- 传蒋凡调任阿里大文娱,阿里巴巴:系谣言

- 激光技术能否打开电子产品使用坚硬材料的大门?

- 被时代淘汰的银行柜员:跟不上科技的改革,终究会面临失业

- 美国死亡破4万,苹果谷歌要慌?硅谷可能“暴雷”,华为联手中芯大动作

- 张大奕“被小三”后续:阿里否认把总裁蒋凡降职到边缘部门

- 美担心半导体被卡脖子?台积电拒入美建厂,并提出三大要求

- 你们觉得去年华为说的鸿蒙系统是“空城计”吗?看网友回答

- 程序员怒斥:资本重视短期利益,牛点的都转管理,不牛的35岁下课

- 天猫总裁夫人怒怼张大奕被删,马云:让反对阿里的都消失?

- 为什么苹果手机越卖越便宜,安卓越来越贵,这背后是什么原因?

- 谷歌宣布消息,联合三星打造自研芯片,小米面临巨大压力?

- 黑小马通讯:第五期京东无货源店群线下交流学习会圆满落幕

- 美国边境公司的车牌扫描技术制造商被黑客洗劫一空?

- 网曝苹果销量下降36%?iPhone 12跳票基本实锤

- 苹果:全球最赚钱的公司,超过1万元的手机,净利润是多少?

- 郭台铭的王牌不只是富士康,还有大陆这家工厂,排名位居世界第二

- 库克猝不及防,京东突然宣布,新iPhone未售先“降价”,iPhone12也躺枪

- 手机处理器哪家强?落寞的联发科,仍然拿下24%的市场份额!

- 最低2799元,iPhone降维打击来了

- 惊艳!国内三大手机巨头东莞新研发总部办公楼纷纷亮相!

- 老员工提离职,老板涨1千工资留人,隔天人事发来信息,看完愣了

- 公司大裁员,却唯独给他升职加薪,他做对了什么?

- 一加8销售额1分钟破亿?刘作虎直言:小屏旗舰没有比它更好的了

- 三星Note 20曝光参数 4000mAh电池+骁龙865 Plus

- 天猫总裁夫人喊话张大奕,阿里将正式进行调查

- 阿里“太子”蒋凡与张大奕绯闻再发酵,阿里:认真反思、进行调查

- 拒绝再被卡脖子?华为不再完全依赖台积电,悄然倒向中芯国际

- 工作1个月离职,却要赔偿公司95210元,网友:被骗去博彩公司了吧

- 公司聚餐,90后女白领拿饮料找主管敬酒,被公司开除

- 华为居然道歉了?华为都弯腰了?我们的青春结束了

- 如果苹果离开中国市场会怎么样?郭台铭:将会有大量企业倒闭

- 想畅快吃鸡?这些“物理外挂”是你的不二之选!

- 确认!吉利将制造火箭 建立自己导航系统 这是要上天啊

- 又一国产机皇诞生?一加8Pro参数曝光:无线充电+2K120Hz共存屏幕

- 下岗女员工:去餐饮店面试收银员,刚开始挺顺利,可看了身份证就说不用来了

- “那一夜,月亮分出叉,并燃烧起来”:1178,坎特伯雷事件

- 要和高通说再见了,谷歌宣布一大消息,华为又将迎来对手

- 海外巨头难剿TikTok

- 数字货币真的要来了?支付宝和微信会被取代吗?

- 富士康转战印度后,苹果又公布了一个大消息,中国网友:慢走不送

- 为什么很多公司自己不直接交社保,而是找代理公司交社保?

- MS员工炫耀:入职外企一周,不到6点下班,太安逸,想离职跑路了

- “裁完员工40人,现在轮到裁自己!”

- 又有工厂关闭!富士康面临“无单可接”,郭台铭也会有这一天?

- 大数据称盖茨深陷病毒“阴谋论”:他制造了病毒 为从疫苗中获利

- 口罩大“屠杀”,多家物流公司紧急停收所有医用防疫物资!

- “5G消息”来了!手机短信不再只接收验证码,还可以视频、群聊、买车票